在模擬CMOS集成電路設(shè)計(jì)中,MOS晶體管的輸出電阻(Rout)和溝道長(zhǎng)度(L)是兩個(gè)關(guān)鍵參數(shù),它們直接影響電路的性能,如增益、帶寬和功耗。本文基于仿真設(shè)計(jì)的基礎(chǔ)知識(shí),探討Rout與L的關(guān)系及其在設(shè)計(jì)中的應(yīng)用。

MOS管的輸出電阻Rout是衡量其輸出端對(duì)電壓變化敏感度的重要指標(biāo)。在高增益放大器(如共源放大器)中,Rout與電路的電壓增益直接相關(guān),增益Av ≈ gm × Rout,其中g(shù)m是跨導(dǎo)。因此,提高Rout可以有效提升增益。在實(shí)際設(shè)計(jì)中,Rout通常受溝道長(zhǎng)度調(diào)制效應(yīng)影響,其值近似為Rout ≈ 1 / (λ × ID),其中λ是溝道長(zhǎng)度調(diào)制參數(shù),ID是漏極電流。

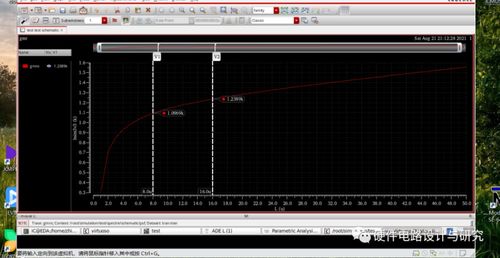

溝道長(zhǎng)度L在CMOS工藝中是一個(gè)可調(diào)參數(shù),對(duì)Rout有顯著影響。隨著L的增加,溝道長(zhǎng)度調(diào)制效應(yīng)減弱,λ減小,從而導(dǎo)致Rout增大。例如,在長(zhǎng)溝道器件中,Rout較高,適用于高增益應(yīng)用;但L增大會(huì)降低晶體管的截止頻率(fT),影響電路的速度和帶寬。反之,短溝道器件(L較小)具有更高的速度和更低的功耗,但Rout較低,可能限制增益性能。

在仿真設(shè)計(jì)中,工程師需要權(quán)衡Rout與L的關(guān)系。例如,在運(yùn)算放大器設(shè)計(jì)中,通過(guò)調(diào)節(jié)L來(lái)優(yōu)化增益和帶寬的折衷。使用仿真工具(如SPICE)可以分析不同L值下Rout的變化,并驗(yàn)證電路性能。工藝變異對(duì)L和Rout的影響也需在仿真中考慮,以確保設(shè)計(jì)的魯棒性。

理解MOS管的Rout與L的相互作用是模擬CMOS集成電路設(shè)計(jì)的基礎(chǔ)。通過(guò)合理選擇L值,并結(jié)合仿真優(yōu)化,可以實(shí)現(xiàn)高性能、低功耗的電路設(shè)計(jì),滿足現(xiàn)代電子系統(tǒng)的需求。